Scientists at Forschungszentrum Jülich and RWTH Aachen Universitywant to create a leading international location for neuromorphic AI hardwaretogether with companies from the region.

Establishing a technological basis for neuroinspired AI hardware from Europe – that is the goal of the NeuroSys future cluster and the NEUROTEC project, where Forschungszentrum Jülich and RWTH Aachen University are cooperating with each other. To this end, an internationally leading location for neuromorphic hardware – computer chips inspired by the human brain – is to be created in the Jülich-Aachen region in collaboration withlocal high-tech companies. Following a meeting at the Jülich-Aachen Neuromorphic Computing Day, which took place at Forschungszentrum Jülich on May 24, 2022, the researchers are now providing an insight into the interim status of the projects.

NEUROTEC entered its second phase at the end of 2021 and will receive total funding of around 36 million euros over five years from the German Federal Ministry of Education and Research (BMBF). The future cluster “NeuroSys – Neuromorphic Hardware for Autonomous Artificial Intelligence Systems” had prevailed in last year’s Clusters4Future ideas competition and will receive up to 45 million euros in funding from the BMBF.

In this interview, Prof. Rainer Waser of Forschungszentrum Jülich and RWTH Aachen University, coordinator of NEUROTEC (Neuro-inspired Technology of Artificial Intelligence for Future Electronics) together with Prof. Max Christian Lemme of RWTH Aachen University and AMO GmbH, coordinator of the future cluster NeuroSys (Neuromorphic Hardware for Autonomous Systems of Artificial Intelligence) explain the current status of developments.

Prof. Rainer Waser, what exactly do we need such neuromorphic computer chips modeled on the human brain for?

Prof. Rainer Waser: In NEUROTEC, we are focusing on a promising area of the future, namely hardware for artificial intelligence applications. With our approach, we are addressing a very fundamental problem, the energy problem: Because the use of AI is currently still very energy-intensive. The training of models is usually done on supercomputers and requires more and more computing time. Every 3 to 4 months the computational effort doubles, at least this is the trend of the last years.

Neuromorphic systems with artificial synapses promise to solve these tasks much more efficiently – by several orders of magnitude – than is possible with conventional digital computers. In the long term, a wide range of applications is conceivable: from the smallest nanosensors, the “smart dust”, to intelligent implants with energy-autonomous AI control, pattern recognition chips in mobile devices, online-trainable controllers in Industry 4.0, vehicle-based AI electronics for autonomous driving, to mainframe computers that in turn emulate the brain or centrally solve complex AI tasks for the surrounding economy.

The NEUROTEC project is funded by the “Sofortprogramm für den Strukturwandel”. It is intended to help create new jobs in the Rhenish mining region even before the end of coal mining. What exactly do you have in mind?

Prof. Rainer Waser: We plan to support local industry, particularly in the area of basic technologies. The professional sectors that we are addressing extend far beyond actual chip production. This also includes, for example, plant engineering, measurement technology and electronics development. The NEUROTEC II project phase has got off to a very good start since November 2021 and almost all work packages are on schedule. Some work packages are even slightly ahead of their time.

The technology is currently still in the research and development phase. Nevertheless, there are already some initial concrete successes to report. Naturally, these are initially primarily jobs for specialized staff, before the technology matures and the focus shifts to industrial production, when the technology becomes widely used. A current example: Prof. Heuken from AIXTRON SE highlightedat the Jülich-Aachen Neuromorphic Computing Day the prospects that will open up in the next few years in terms of new jobs at AIXTRON in connection with the new 2D materials. These materials are being investigated in the NEUROTEC project for their suitability for neuromorphic computing.

What are the advantages of this neuromorphic hardware you are developing?

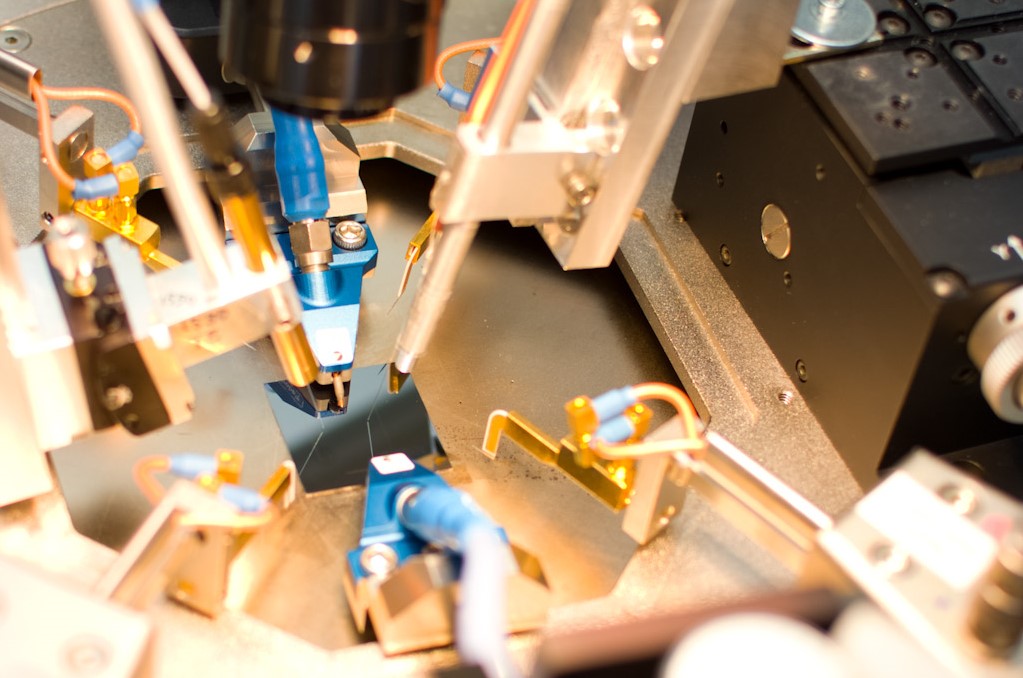

Prof. Rainer Waser: Conventional computer chips are based on transistors. We would like to supplement these transistors with a novel memristive component. Such a “resistor with memory” resembles the synapses in natural nerve cells and is therefore particularly suitable for artificial neuronal networks, such as those used for artificial intelligence applications.

An important feature of neuromorphic chips is that computing processes and memory are no longer physically separated. The data transfer between processor and memory that takes place continuously on conventional computers with so-called Von Neumann computer architecture is extremely energy-intensive and slows down computations. In contrast, we envision neuromorphic chips with artificial synapses that can do both: Store information and process it at the same time. Computing is then performed directly in – non-volatile – memory; this is also known as computing-in-memory. And it makes it possible to process information in a highly parallel manner. The model here is actually the human brain, which requires an average of just 20 Watt. That is several orders of magnitude less than the energy requirements of a supercomputer that performs similar functions using AI.

Prof. Max Christian Lemme, in the NeuroSys future cluster, you are driving forward complementary developments in the field of neuromorphic hardware. The topic is also being intensively pursued globally. Where does the region stand in terms of global competition?

Prof. Max Christian Lemme: The BMBF’s Future Cluster Initiative has the explicit goal of quickly translating excellent cutting-edge research into applications, and doing so in regional alliances. To achieve this, we have brought together researchers along the entire value chain in the NeuroSys future cluster who have worldwide visibility in their respective disciplines. In addition, there are regional companies and start-ups from the high-tech sector. We now cover the entire field from new materials to image and speech processing and medical technology, and expand the concept with socio-economic issues – i.e. research on the ethics of AI, on consequences for the job market and on viable business models for “AI Hardware Made in Europe”.

An advisory board of scientists and international companies completes the cluster. So, I dare to say that we are on par with the global competition. What is missing in the region is a modern semiconductor factory for AI chips, the location of which we have formulated in our vision. With the excellently trained engineers and scientists in the region, including Belgium, the Netherlands and the Ruhr area, the proximity to the research institute IMEC in Belgium and the leading manufacturer of lithography equipment ASML in the Netherlands, we have an excellent argument.

How far has the technology come?

Prof. Max Christian Lemme: As is often the case, there is no simple answer. It is already possible to produce special neuromorphic chips using conventional technology. However, these are still far from the energy efficiency of the brain. Here, the new technologies from resistive switching oxides, phase change materials or even 2D materials can take us much further. However, their use is always a question of industrial manufacturability. This varies from material to material, and it currently looks as if each generation of new materials will also bring a boost in efficiency. It is therefore very important to already be working closely on the two projects with manufacturers of material deposition systems such as Aixtron from Herzogenrath or deep tech start-ups such as Black Semiconductor or Aixscale Photonics.

In parallel, however, the Future Cluster is also working with industry at the higher levels of the value chain. Here, there are several start-ups in the region such as Clinomic Medical, Gremse-IT or a company co-founded by my RWTH Aachen colleague Prof. Rainer Leupers shortly after the NeuroSys launch. So, we are already working on all technology levels to realize the goals and are still in the acceleration phase after an excellent flying start!

More information:

www.neurotec.org

https://www.neurosys.info

Peter Grünberg Institut, Elektronische Materialien (PGI-7)

Forschungsschwerpunkt Neuromorphes Computing

https://www.eld.rwth-aachen.de/go/id/psfz/

Video: https://www.youtube.com/watch?v=tJghcXPby48

Contactperson:

Prof. Dr. Rainer Waser

Koordinator NEUROTEC, Peter Grünberg Institut für Elektronische Materialien (PGI-7), Forschungszentrum Jülich

Tel: 02461 61-5811

E-Mail: r.waser@fz-juelich.de

Prof. Dr. Ing. Max C. Lemme

Koordinator NeuroSys, Lehrstuhl für Elektronische Bauelemente, RWTH Aachen University

Tel: 0241 80 20280

Email: neurosys@eld.rwth-aachen.de

Media contact:

Dr. Regine Panknin

Unternehmenskommunikation

Tel.: 02461 61-9054

E-Mail: r.panknin@fz-juelich.de