Successful Patrick Fay DL on III-N Nanowire FETs for Low-Power-Applications

The distinguished lecture on III-N Nanowire FETs for Low-Power-Applications was held on November 23, 2020. It was organized by the EDS Germany Chapter and co-sponsored by the NanoP from THM – University of Applied Sciences. The DL was attended by 17 participants, with 9 IEEE participants and 8 guests.

The IEEE DL was opened by Prof. Mike Schwarz, ED Germany Chapter chair. He kindly introduced Prof. Fay from the University of Notre Dame, Indiana, USA and the participants.

Prof. Fay started with a motivation of III-N compounds application in low power system applications. He pointed out that heterogeneous integration of III-N FETs sets new challenging fields for researchers. The question arises, if GaN can play a role in low power systems? The speaker continued with some background information and properties of GaN and III-N semiconductors. He presented their advantages and challenges. It is well known that material characteristics strongly influence the device parameters. However, a key factor determining applicability of III-N FETs in low power applications is low enough subthreshold slope of the transistor characteristics. This requirement is common for all the field-effect devices in low power solutions. If achieved then not only logic, but also analog and further emerging applications can benefit from the superior III-N properties.

Prof. Fay continued and presented GaN-based nanowires for low power applications. He offered GaN nanowire FETs, details on the process, e.g. material growth, oxide deposition, etc. Furthermore, the lecturer discussed the gate capacitances for c- and m-plane substrates. Afterwards, experimental results as transport characteristics and output characteristics with remarkable on-current of 130µA/µm and with Ion/Ioff ratio larger than 108 were presented. Possible enhancements of the devices were also shown.

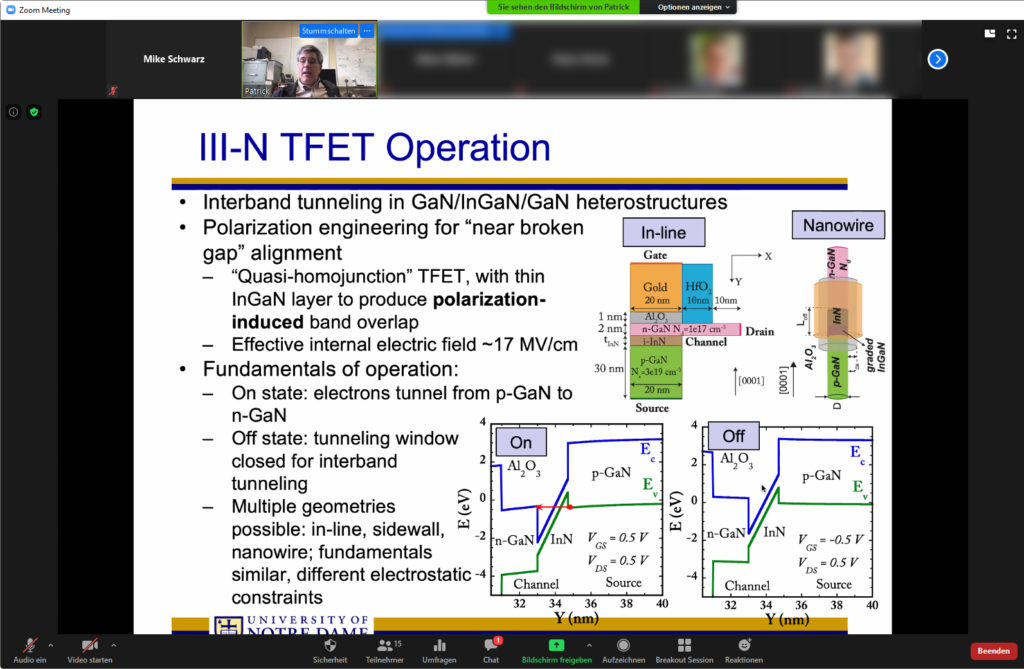

A second part of the lecture dealt with TFETs made of III-N semiconductors. After a short introduction into the basic principles, Prof. Fay promised such devices to be another option for low power solutions. He referred to TFET design possibilities and showed some simulation results for GaN/InGaN/GaN heterostructures and their TFET performances. Further investigations of III-N Nanowire TFET scalability were presented. Finally, the speaker showed actual experimental results of such III-N Nanowire TFET, published in 2020 by A. Chaney et al. at Cornell.

After the presentation several questions allowed for a fruitful discussion on various topics. A huge “Thank you” to all participants and Patrick Fay.