Successful Adrian Ionescu DL on Electronic devices operating near 100 millivolts

The distinguished lecture on “Electronic devices operating near 100 millivolts” was held on February 1, 2021. It was organized by the EDS Germany Chapter and co-sponsored by the NanoP from THM – University of Applied Sciences. The DL was attended by 16 IEEE participants.

The distinguished lecture of Prof. Ionescu from EPFL (Switzerland), started with an introduction into the topic “Towards energy efficient semiconductor technologies for Edge AI”. The speaker gave some initial examples of successors of low power devices e.g. the iPhone, a wireless computer with sensors. These examples combine energy efficiency with new functionalities. Furthermore, Prof. Ionescu took a focus on a so-called “Dark Silicon”, which allows high transistor densities with actual high-end technology nodes by keeping e.g. 80% of the transistor silent, while 20% perform calculations. Such strategies allow controlling warming by the power dissipation and require the parallelism by multi-core systems. Nature and the human brain are idols in terms of dark systems. However, such strategies are approaching the sweet spot, where the N cores (128 cores) require more effort in organization, which finally cost performance gain of the parallelism.

To overcome these limitations, new device concepts as the Tunnel FETs allow operating near the 100mV supply bias and improving the power dissipation issue by switching with steep slopes. Prof. Ionescu and his group at EPFL did pioneering work in this field and still improve and combine these devices with further concepts. He stated different potentials to optimize TFETs further, e.g. high-k dielectrics, narrower junction, thinner body, etc. Furthermore, Prof. Ionescu offered the best experimental Tunnel FET so far from University Lund, a vertical heterostructure InAs/GaAsSb/GaSb Tunnel FET with an Ioff=1nA/µm, Ion=10.6µA/µm at Vdd=0.3V and a subthreshold slope of 44mV/dec @50mV and 48mV/dec @300mV. Effects of TAT on Tunnel FETs characteristics were discussed and the effect of cancellation at low temperature (<100K).

After intense discussion on the TFETs, a combination of TFETs and MOSFETs on the same 2D material, WSe2 flakes, showed potentials in various performance parameters. Moving forward, the Negative Capacitance Devices were highlighted by Prof. Ionescu and it potentials as technology booster for MOSFETs and Tunnel FETs down to 2nm. He offered Negative Capacitance TFET (NC-TFET) results from the collaboration of IMEC and EPFL with an improved subthreshold slope of sub-60 over about 3 decades. Further examples followed, e.g. “Si-doped HfO2 on NW Tunnel FET Array”, “Subthermionic NC FET biosensor” and more.

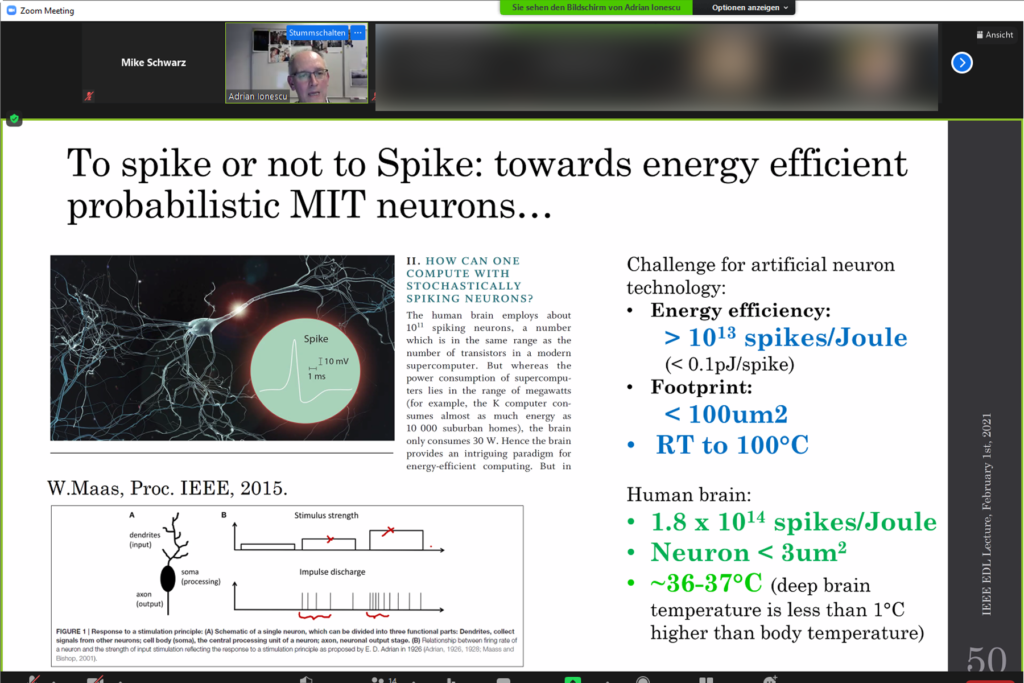

Finally, Prof. Ionescu discussed the potentials of steep slope and energy efficiency in phase change VO2 devices for neuromorphic applications (MIT).

After the lecture, an intense discussion followed, e.g. the increasing impact of tolerances and variability while moving towards the 100mV regime, which acts inverse proportional, but requires extensive analyses. Discussion on the conditions to achieve the TAT suppression at 100K followed and further questions were answered by Prof. Ionescu.